ISE軟件的使用指南

ISE(Integrated Software Environment)軟件是一款廣泛用于可編程邏輯器件(如FPGA和CPLD)開發(fā)的集成開發(fā)環(huán)境,尤其常見于Xilinx公司的芯片設(shè)計流程中。它提供了從設(shè)計輸入、綜合、實現(xiàn)到下載的全套工具,幫助工程師高效完成數(shù)字電路設(shè)計。本文將介紹ISE軟件的基本使用方法,包括安裝、項目創(chuàng)建、設(shè)計流程和調(diào)試技巧。

一、安裝與配置

ISE軟件的安裝相對簡單。用戶需從Xilinx官網(wǎng)下載適合自己操作系統(tǒng)的版本(如Windows或Linux),并按照安裝向?qū)е鸩讲僮鳌0惭b過程中,建議選擇完整安裝以獲取所有必要組件,如綜合工具XST和仿真工具ISim。安裝完成后,首次啟動時可能需配置許可證文件,確保軟件功能完整。

二、創(chuàng)建新項目

啟動ISE后,第一步是創(chuàng)建新項目。點擊“File”菜單中的“New Project”,輸入項目名稱和存儲路徑。接著,選擇目標設(shè)備類型(如FPGA型號)、設(shè)計流程(如HDL)和默認語言(如VHDL或Verilog)。完成后,ISE會自動生成項目結(jié)構(gòu),用戶可通過“Add Source”導(dǎo)入現(xiàn)有設(shè)計文件或創(chuàng)建新文件。

三、設(shè)計輸入與綜合

ISE支持多種設(shè)計輸入方式,包括HDL代碼編輯、原理圖繪制和IP核集成。在代碼編輯器中編寫VHDL或Verilog代碼后,使用“Synthesize”工具進行綜合,將高級代碼轉(zhuǎn)換為門級網(wǎng)表。綜合過程中,ISE會檢查語法錯誤和邏輯問題,用戶可通過日志窗口查看警告和錯誤信息,及時修正。

四、實現(xiàn)與布局布線

綜合完成后,進入實現(xiàn)階段。點擊“Implement Design”工具,ISE會執(zhí)行翻譯、映射和布局布線操作,將網(wǎng)表適配到具體硬件。用戶可在此階段設(shè)置約束文件(如時鐘頻率和引腳分配),以優(yōu)化性能。實現(xiàn)后,ISE會生成報告,顯示時序分析和資源利用率,幫助用戶評估設(shè)計質(zhì)量。

五、仿真與調(diào)試

在設(shè)計過程中,仿真至關(guān)重要。ISE內(nèi)置ISim仿真工具,用戶可創(chuàng)建測試平臺文件,模擬設(shè)計行為。通過“Simulate Behavioral Model”運行仿真,觀察波形圖以驗證功能。如果發(fā)現(xiàn)問題,可使用調(diào)試工具如ChipScope進行在線調(diào)試,實時監(jiān)控信號。

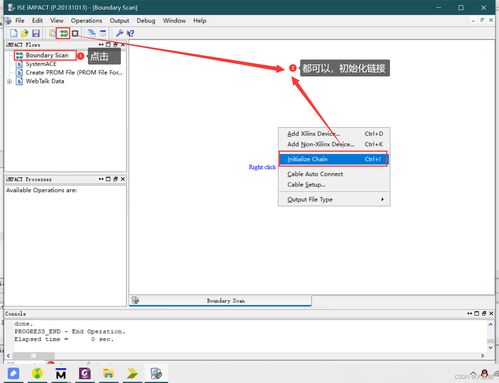

六、生成比特流與下載

設(shè)計驗證無誤后,生成比特流文件。點擊“Generate Programming File”,ISE會創(chuàng)建用于配置FPGA的.bit文件。通過JTAG或?qū)S秒娎|將文件下載到目標設(shè)備,完成整個開發(fā)流程。

ISE軟件作為經(jīng)典的FPGA開發(fā)工具,以其強大的功能和直觀的界面,降低了數(shù)字設(shè)計的門檻。掌握其基本使用流程,包括安裝、設(shè)計、仿真和下載,是硬件工程師的必備技能。建議初學(xué)者多練習(xí)示例項目,并參考官方文檔以深入理解高級功能。

如若轉(zhuǎn)載,請注明出處:http://www.mennsa.com/product/222.html

更新時間:2025-12-26 18:53:29